## 1. Description

The PID3190A are high-performance Smart Power Stage (SPS) with 90A peak current capability. They contain high-side and low-side N-Channel MOSFETs and a synchronous buck driver IC. The driver IC integrates high accuracy current sense, temperature sense, comprehensive protection mechanism.

The PID3190A internal current sense is based on drain source voltage (VDS) of both high-side and low-side MOSFET current, using algorithm with temperature compensation and inductance calibration to achieve superior current sense accuracy and lower propagation delay. Protections include cycle-by-cycle over current protection with programmable thresholds, VCC/VDRV UVLO protection, phase fault detection, IC temperature reporting and thermal shutdown. Operation frequency is up to 1.2MHz at steady state and 4MHz at transient state, providing high performance transient response.

The PID3190A are offered in 5mm x 6mm DFN package, which is optimized for high-current application and can greatly reduce parasitic and SW ringing, as well as provide excellent heat transfer path.

## 2. Typical Applications

- High current, high frequency DC-DC converters

- Voltage Regulators for CPUs, GPUs, and DDR memory arrays of Desktop & Notebook Microprocessors

- Routers, Switches and other ASICs

## 3. Features

- Internal high accuracy and low delay current sense

- 30V(HS)/25V(LS) breakdown voltage of MOSFETs for higher robustness reliability

- Operating frequency up to 1.2MHz for steady state, 4MHz for transient state

- Peak output current capability up to 90A

- Responds properly to Tri-state PWM input

- Precise output current monitoring of 5µA/A

- Precise temperature monitoring of 8mV/°C

- Support switch node fault detection and flag

- Cycle-by-cycle over current protection

- OCP and thermal shutdown with fault flag

- 5mm x 6mm x 0.9mm DFN-39 package

- Catastrophic Fault Detection

- a. Over-temperature Protection

- b. Over-current protection (POCP & NOCP)

- c. UVLO on VCC and VDRV

- d. High-side and low-side MOSFET short e. UVLO on BOOT-PHASE

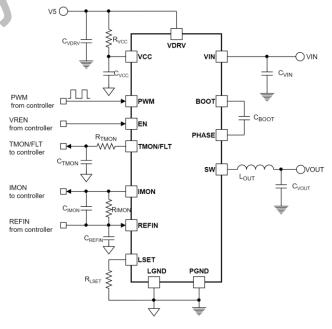

## 4. Application Diagram

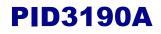

Figure 1. Typical Application Diagram

Potens semiconductor corp.

## 5. Order Information

| Part Number | Package Type | Package Qty | MSL | POCP |

|-------------|--------------|-------------|-----|------|

| PID3190A    | DFN5X6-39L   | 5000        | 1   | 120A |

## 6. Package Reference and Pin Functions

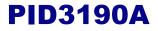

Figure 2. DFN5X6-39L Package(Top View)

xxxxxxxx: Date Code

#### Figure 3. PID3190A Top Marking

| P | Pin #            | Name  | Description                                                                                                                                                                                      |

|---|------------------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   | 1                | I.C.  | Internal connection, can be left floating or connected to VOUT.                                                                                                                                  |

|   | 2                | LGND  | Signal ground. All signals are referenced to this pin.                                                                                                                                           |

|   | 3                | VCC   | Bias voltage for control logic. Connect a X7R 1 $\mu$ F ceramic capacitor between VCC and LGND and a 1 $\Omega$ resistor between VCC and VDRV pins.                                              |

|   | 4                | VDRV  | The supply of gate driver. Connect a X7R $1\mu$ F cap between VDRV and PGND. VDRV should be connected to +5V power supply.                                                                       |

|   | -9, 20-<br>4, 40 | PGND  | Power ground. It is also the power ground of the low-side MOSFET.                                                                                                                                |

| e | 6,41             | GATEL | Low-side MOSFET driver pin that can be connected to a test point in order to observe the waveform.                                                                                               |

| 1 | 0-19             | SW    | Switching node of synchronous buck converter.                                                                                                                                                    |

| 2 | 5-30             | VIN   | 4.5V to 16V high current input voltage connection. Place at least one 1 $\mu$ F X7R capacitor between VIN pin and PGND pin. Also connect two 10 $\mu$ F X7R /X6S ceramic capacitors in parallel. |

|   | 31               | NC    | No connection, leave the pin unconnected or short to VIN.                                                                                                                                        |

# **PID3190A**

| 32                          | PHASE    | Switching node. For bootstrap capacitor connection only.                                                                                                                                                                                                                                                                                                                                              |

|-----------------------------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 33                          | BOOT     | Bootstrap capacitor connection. Connect a minimum 0.22 $\mu$ F X7R ceramic capacitor from BOOT to PHASE pin. The bootstrap capacitor provides the charge to turn on the high-side MOSFET. For applications with VIN greater than 14V, use a 2 $\Omega$ resistor in series with the bootstrap capacitor to reduce excessive voltage spike at SW node.                                                  |

| 34                          | PWM      | 3.3V/5V logic level PWM input. PWM input: "High" turns high-side MOSFET<br>on and low-side MOSFET off; "Tri-state" turns both MOSFETs off; "Low" turns<br>the low-side MOSFET on and high-side MOSFET off.                                                                                                                                                                                            |

| 35                          | EN       | Pulling EN high enables the driver; pulling EN low disables the driver and<br>enters ultralow quiescent current mode. Floating this pin is not recommended<br>however a low current pull-down is embedded to keep the driver off if the pin<br>is floating. The EN Pin is VCC tolerant.                                                                                                               |

| 36                          | TMON/FLT | The voltage at this pin is defined by the equation 8mV * (Celsius Temperature) + 0.6V. This pin will be pulled up to 3.3V under severe over temperature, over current, phase fault, BOOT-PHASE UVLO, etc. Refer to Fault Reporting and Identification table for more details. Connect a 10nF decoupling cap between this pin and GND, only 1pcs decoupling cap is needed for multi-phase application. |

| 37                          | LSET     | A resistor from this pin to LGND pin sets the inductor value for the internal current sensing circuitry. $100k\Omega$ for $100nH$ ; Float for $210nH$ ; < $10k\Omega$ (or GND) for $120nH$ . Leave it floating or short to GND if not used this function.                                                                                                                                             |

| 38                          | IMON     | Sensed current output signal referenced to the REFIN pin or a reference voltage. Current on IMON pin represents inductor current information at $5\mu$ A/A.                                                                                                                                                                                                                                           |

| 39                          | REFIN    | The reference supply voltage for the IMON information. This pin has a low bias current and can be tied to a fixed voltage between 1.1V and 1.9V such as bias rails from a PWM controller. Use a X7R $0.1\mu$ F ceramic capacitor between REFIN and a quiet GND near PWM controller. Can be left floating if not used.                                                                                 |

| <i><b>Q</b><sup>(</sup></i> | 2        |                                                                                                                                                                                                                                                                                                                                                                                                       |

## 7. Specifications

#### 7.1 Absolute Maximum Ratings Note(1)

|                         |                                               | Min  | Мах     | Unit |

|-------------------------|-----------------------------------------------|------|---------|------|

| VIN                     |                                               | -0.3 | 25      | V    |

| VCC, VDRV               |                                               | -0.3 | 6       | V    |

| SW, PHASE               | DC                                            | -0.3 | 25      | V    |

|                         | Repetitive pulse Note(2)                      | -5   | 25      | V    |

| VIN-PHASE               |                                               | -0.3 | 25      | V    |

|                         | Repetitive pulse Note(2)                      | -0.3 | 30      | V    |

| BOOT-GND                | DC                                            | -0.3 | 31      | V    |

| BOOT-PHASE              | DC                                            | -0.3 | 6       | V    |

| All other Pins          |                                               | -0.3 | VCC+0.3 | V    |

|                         | Lead Temperature (Solder)                     |      | 260     | °C   |

| TJ                      | Virtual junction temperature range            | -40  | 150     | °C   |

| T <sub>STG</sub>        | Storage temperature range                     |      | 150     | °C   |

| Notes:                  |                                               |      |         |      |

| (1) Exceeding these rat | ings may cause permanent damage to the device |      |         |      |

(2) Repetitive pulse ≤15 ns. Verified at bench characterization

#### 7.2 ESD Ratings

|                                |                  |                                                                                    | Value               | Unit |

|--------------------------------|------------------|------------------------------------------------------------------------------------|---------------------|------|

|                                |                  | Human body model (HBM), per<br>ANSI/ESDA/JEDEC JS-001 <sup>Note(1)</sup>           | ±1                  | kV   |

| V <sub>ESD</sub> Electrostatic |                  |                                                                                    |                     |      |

|                                | discharge        | Charged device model (CDM), per JEDEC specification JESD22-C101 <sup>Note(2)</sup> | ±1                  | kV   |

| Notes:                         |                  |                                                                                    |                     |      |

| (1) JEDEO                      | C document JEP15 | states that 500V HBM allows safe manufacturing with a standard                     | ESD control process |      |

| (2) JEDEO                      | C document JEP15 | states that 250V CDM allows safe manufacturing with a standard                     | ESD control process |      |

|                                |                  |                                                                                    |                     |      |

Potens semiconductor corp.

#### 7.3 Recommended Operating Conditions

|                              |                                                          | Min  | Max   | Unit |

|------------------------------|----------------------------------------------------------|------|-------|------|

| VIN                          |                                                          | 4.5  | 16    |      |

| VCC, VDRV                    |                                                          | 4.5  | 5.5   | V    |

| REFIN                        |                                                          | 1.1  | 1.9   |      |

| IMON                         | IMON Output Range                                        | 0.8  | VCC-2 | V    |

| Fsw                          |                                                          | 200  | 1200  | kHz  |

| Fsw                          | During Transient                                         |      | 4000  | kHz  |

| Тј                           |                                                          | -40  | 125   | °C   |

| Note:<br>The device is not g | uaranteed to function outside of its operating condition | ons. |       | 5    |

## 7.4 Thermal Information

|                       | Thermal Metric                            | Values | Unit |

|-----------------------|-------------------------------------------|--------|------|

| R <sub>0JA</sub>      | Junction-to-air thermal resistance        | 21     | °C/W |

| R <sub>0JC(TOP)</sub> | Junction-to-case (top) thermal resistance | 20.4   | °C/W |

| <b>R</b> өјс(воттом)  | Junction-to-case (bot) thermal resistance | 0.2    | °C/W |

Potens semiconductor corp.

## 8. Electrical Characteristics

The electrical characteristics involve the spread of values guaranteed within the recommended operating conditions. Typical values represent the median values, which are related to  $T_J = 25^{\circ}C$ , VCC=VDRV=5V, REFIN = 1.2V, Fsw  $\leq$  1.2 MHz (unless otherwise specified).

| Parameter                                   | Symbol              | Conditions                                              | Min | Тур. | Max | Unit |

|---------------------------------------------|---------------------|---------------------------------------------------------|-----|------|-----|------|

| PWM                                         |                     |                                                         |     |      |     |      |

| PWM Input High<br>Threshold                 | V <sub>PWM_HI</sub> | PWM Low or Tri-state to High                            | 2.4 |      |     | V    |

| PWM Input Low<br>Threshold                  | Vpwm_li             | PWM High or Tri-state to Low                            |     |      | 0.8 | v    |

| Tri-state Voltage<br>Rising Threshold       | Vtri_hi             | Rising from Tri-state to leaving<br>Tri-state           | 2.1 | 2.2  | 2.3 | V    |

| Tri-state Voltage falling Threshold         | Vtri_lo             | Falling from Tri-state to leaving<br>Tri-state          | 0.9 | 1    | 1.1 | V    |

| PWM High<br>Propagation<br>Delay            | tdelay_pwm_hi       | Measured from PWM rising edge to GATEL starts to fall   | 9.5 | 14   | 17  | ns   |

| PWM Low<br>Propagation<br>Delay             | tdelay_pwm_lo       | Measured from PWM falling<br>edge to SW starts to fall  | 23  | 40   | 56  | ns   |

| Tri-state to High<br>Propagation<br>Delay   | tdelay_tri_hi       | PWM Tri-state to High transition<br>to SW>1V            | 15  | 21   | 26  | ns   |

| Tri-state to Low<br>Propagation<br>Delay    | tdelay_tri_lo       | PWM Tri-state to Low transition<br>to GATEL>1V          |     | 11   | 24  | ns   |

| Tri-state Hold<br>Off Time from<br>PWM High | Ttrihold_h2t        | PWM High to Tri-state transition<br>to SW starts fall   | 49  | 61   | 73  | ns   |

| Tri-state Hold<br>Off Time from<br>PWM Low  | TTRIHOLD_L2T        | PWM Low to Tri-state transition<br>to GATEL starts fall | 26  | 32   | 38  | ns   |

| PWM Input Tri-<br>state Float<br>Voltage    | Vpwm_float          | PWM Input Floating                                      | 1.6 | 1.7  | 1.8 | V    |

| Pulled up<br>Impedance Note(1)              | Rpwm_up             | Controlled by EN & VCC_POR<br>& VDRV_POR                |     | 19   |     | kΩ   |

Potens semiconductor corp.

# **PID3190A**

| Pulled down<br>Impedance Note(1)RPWM_DOWNAlways enabled10Minimum PWM<br>High/Low Pulse<br>for Safe<br>Operation Note(1)tewm_HigLO_MINRequirement on controller PWM<br>output5050Minimum PWM<br>Tri-state Time<br>for Safe<br>Operation Note(1)tewm_TRI-STATE_MINRequirement on controller PWM<br>output5050Minimum PWM<br>Tri-state Time<br>for Safe<br>Operation Note(1)tewm_TRI-STATE_MINRequirement on controller PWM<br>output5050GATEL Pull<br>Down<br>ResistanceRGL_PULLDNPWM=Tri-state284663HS minimum<br>turn on time<br>Note(1)ToN_MIN_HSSW rising 10% to falling 10%50 | kΩ<br>ns<br>ns<br>kΩ<br>ns |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

| High/Low Pulse<br>for Safe<br>Operation Note(1)tpwm_Hi&LO_MINRequirement on controller PWM<br>output5050Minimum PWM<br>Tri-state Time<br>for Safe<br>Operation Note(1)tpwm_TRI-STATE_MINRequirement on controller PWM<br>output5050GATEL Pull<br>Down<br>ResistanceRGL_PULLDNPWM=Tri-state284663HS minimum<br>turn on time<br>Note(1)TON_MIN_HSSW rising 10% to falling 10%5050                                                                                                                                                                                                  | ns<br>kΩ                   |

| Tri-state Time<br>for Safe<br>Operation Note(1)tpwm_TRI-STATE_MINRequirement on controller PWM<br>output5050GATEL Pull<br>                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                            |

| Down RGL_PULLDN PWM=Tri-state 28 46 63   Resistance HS minimum TON_MIN_HS SW rising 10% to falling 10% 50 50                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                            |

| turn on time T <sub>ON_MIN_HS</sub> SW rising 10% to falling 10%                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | ns                         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | l                          |

| LS minimum turn<br>on time <sup>Note(1)</sup> T <sub>ON_MIN_LS</sub> GATEL Rising 10% to falling 50                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | ns                         |

| Current Sense Output-IMON                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                            |

| Offset     AIMON_OFFSET     0A load, RIMON=1kΩ, 25°C     5     5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | mV                         |

| 0A~30A, R <sub>IMON</sub> =1kΩ -1.5 1.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | А                          |

| Overall Accuracy<br>Note(1)     AIMON_ALL     30A~ 70A, RIMON=1kΩ     -5     +5       VIN=12V, VOUT=0.9V, 800kHz     -5     +5                                                                                                                                                                                                                                                                                                                                                                                                                                                   | %                          |

| GAIN     30A load, R <sub>IMON</sub> =1kΩ, 25 °C     4.8     5     5.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | µA/A                       |

| REFIN Bias<br>Current -1 0 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | μA                         |

| IMON L=120nH, VIN=12V,   Propagation tdeLAY_IMON   Delay Note(1) VOUT=1.8V, Fsw=800kHz, IL   Peak to IMON Peak 30                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ns                         |

| Dynamic range<br>of IMON Note(1) $TA = TJ = -40^{\circ}C \text{ to } 125^{\circ}C, VCC$<br>= 4.5  V to  5.5  V, VIN = 4.5  V - 16<br>V, REFIN=1.2  V     0.8     VCC-2                                                                                                                                                                                                                                                                                                                                                                                                           | V                          |

| Digital Input-EN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                            |

| Enable Power-<br>on Delay t_{DELAY_ENON PWM=0, Measured from EN<br>rising edge to GATEL>1V 10 13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | μs                         |

| Enable Power-<br>off Delay t_DELAY_ENOFF PWM=0, Measured from EN<br>falling edge to GATEL<4V 58 56                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | ns                         |

| Internal Pull-    |                      |                                                                                 |     |      |      |       |

|-------------------|----------------------|---------------------------------------------------------------------------------|-----|------|------|-------|

| down              | Ren_pulldn           | EN is floating                                                                  | 360 | 460  | 557  | kΩ    |

| Resistance        |                      |                                                                                 |     |      |      |       |

| Input High        | V <sub>EN_HIGH</sub> |                                                                                 | 2   |      |      | V     |

| Voltage           | • EN_INGI            |                                                                                 | _   |      |      | •     |

| Input Low         | Ven_low              |                                                                                 |     |      | 0.8  | V     |

| Voltage           |                      |                                                                                 |     |      |      |       |

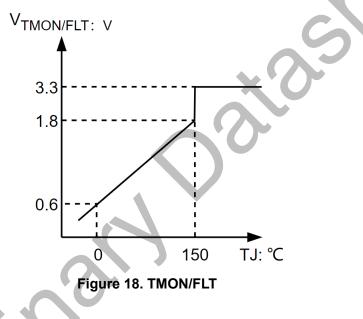

| TMON/FLT-Temp     | erature Sense Outpu  | t and Fault Communication                                                       |     |      |      |       |

| Temperature       |                      |                                                                                 |     |      |      |       |

| Sense Slope       | GTMON_SLOPE          | 0°C <tj<125 td="" ℃<=""><td></td><td>8</td><td></td><td>mV/°C</td></tj<125>     |     | 8    |      | mV/°C |

| Note(1)           |                      |                                                                                 |     |      |      |       |

| Temperature       |                      |                                                                                 |     |      |      |       |

| Sense Offset      | VTMON_OFFSET         | Tj=65°C,0.6V+8mV/°C * Tj                                                        |     | 1.12 |      | V     |

| Voltage Note(1)   |                      |                                                                                 |     |      |      |       |

| TMON Source       |                      |                                                                                 | 436 | 575  | 714  |       |

| Current           | Itmon_source         |                                                                                 | 430 | 575  | /14  | μA    |

| TMON Sink         | -                    |                                                                                 |     |      | 05   |       |

| Current           | Itmon_sink           |                                                                                 | 14  | 20   | 25   | μA    |

|                   |                      | Over-Temperature, Over-                                                         |     |      |      |       |

| FLT Active High   | VFLT_HIGH            | Current, Bootstrap                                                              | 3   | 3.3  | 3.6  | V     |

|                   |                      | Undervoltage, or Phase Fault                                                    |     |      |      |       |

| FLT Active Low    | VFLT_LOW             | No Fault, VCC <uvlo< td=""><td></td><td></td><td>0.28</td><td>V</td></uvlo<>    |     |      | 0.28 | V     |

| FLT mode          | IFLT_SOURCE          | VTMON/FLT=0V                                                                    | 4   | 4.6  | 5.2  | mA    |

| Source Current    | IFET_SOURCE          | VIMON/FLI-OV                                                                    | 4   | 4.0  | 5.2  | IIIA  |

| TMON Active       | * *                  |                                                                                 |     |      |      |       |

| Pull-down         | RTMON_PULLDN         | No Fault, VCC <uvlo< td=""><td>25</td><td>27</td><td>29</td><td>kΩ</td></uvlo<> | 25  | 27   | 29   | kΩ    |

| Resistance        |                      |                                                                                 |     |      |      |       |

| Phase Fault Dete  | ction                |                                                                                 |     |      |      |       |

| LS FET on, HS     |                      | VPHASE-VPGND higher than,                                                       |     |      |      |       |

| FET Short         | VHS_FET_FLT_TH       |                                                                                 |     | 0.85 |      | V     |

| Threshold         |                      | GATEL>1V                                                                        |     |      |      |       |

| TMON/FLT          |                      |                                                                                 |     |      |      |       |

| Delay When HS     | tdelay_hs_flt        | PWM High-Low Cycles to                                                          |     | 1    |      | cycle |

| FET Fault Note(1) |                      | TMON/FLT high                                                                   |     |      |      |       |

| HS FET on, LS     |                      |                                                                                 |     |      |      |       |

| FET Short         | VLS_FET_FLT_TH       | VIN-VPHASE higher than,                                                         |     | 1.75 |      | V     |

| Threshold         |                      | GATEH-VPHASE>1V                                                                 |     |      |      |       |

Potens semiconductor corp.

# **PID3190A**

| TMON/FLT<br>Delay When LS<br>FET Fault <sup>Note(1)</sup>                           | tls_fet_flt                 | PWM High-Low Cycles to<br>TMON/FLT high                                                   |     | 1   |     | cycle |

|-------------------------------------------------------------------------------------|-----------------------------|-------------------------------------------------------------------------------------------|-----|-----|-----|-------|

| Over-Temperature                                                                    | e Protection                |                                                                                           |     |     |     |       |

| Rising<br>Threshold Note(1)                                                         | Trise                       | TMON/FLT pulled up high,<br>Driver Temperature                                            |     | 140 |     | °C    |

| Falling<br>Threshold Note(1)                                                        | TFALL                       | TMON/FLT released<br>Driver Temperature                                                   |     | 120 |     | °C    |

| Cycle-by-Cycle O                                                                    | ver-Current Protection      | on                                                                                        |     | 1   |     |       |

| Positive Peak<br>Over-Current<br>Threshold                                          | loc                         |                                                                                           |     | 120 |     | A     |

| Positive Over-<br>Current<br>Hysteresis                                             | loc_hys                     |                                                                                           | ×   | 10  |     | A     |

| TMON/FLT<br>Delay When<br>OCP                                                       | tdelay_ocp                  | SW High-Low Cycles to<br>TMON/FLT high<br>Continuous 22 to report<br>Continuous 3 to back | 2   | 22  |     | cycle |

| I Limit<br>Comparator<br>Input to Output<br>Propagation<br>Delay <sup>Note(1)</sup> | tdelay_imon_comp            | Input Signal=200mV<br>dv/dt=0.17mV/ns                                                     |     | 60  |     | ns    |

| I Limit Blanking<br>Time Note(1)                                                    | tBLANK_ILIMIT               | De-glitch filter (blanking) time for<br>I Limit comparator trip                           |     | 50  |     | ns    |

| Negative Over-<br>Current Trip Low<br>Level                                         | INOCP                       | SW Low-High Cycles to<br>TMON/FLT high                                                    |     | -50 |     | A     |

| INOCP_HYS<br>Note(1)                                                                | NOCP Hysteresis             |                                                                                           |     | 20  |     | А     |

| VCC and VDRV U                                                                      | Inder Voltage Lockou        | ut                                                                                        | •   | •   |     |       |

| VCC Rising                                                                          | [                           |                                                                                           |     | 4.1 | 4.4 | V     |

| Threshold                                                                           | Vvcc_rising                 |                                                                                           |     |     |     |       |

| -                                                                                   | Vvcc_rising<br>Vvcc_falling |                                                                                           | 3.4 | 3.9 |     | V     |

# **PID3190A**

| VDRV Rising<br>Threshold              | Vvdrv_rising       |                                                                  |     | 4.2  | 4.5 | V  |

|---------------------------------------|--------------------|------------------------------------------------------------------|-----|------|-----|----|

| VDRV Falling<br>Threshold             | Vvdrv_falling      |                                                                  | 3.3 | 3.75 |     | V  |

| VDRV<br>Hysteresis                    | Vvdrv_hys          |                                                                  |     | 0.45 |     | V  |

| Bootstrap<br>Refresh Off<br>Threshold | VBOOT_REFRESH_OFF  |                                                                  |     | 3.7  | 4.0 | v  |

| Bootstrap<br>Refresh On<br>Threshold  | VBOOT_ REFRESH _ON |                                                                  | 3.1 | 3.25 | ~   | V  |

| Bootstrap<br>Refresh<br>Hysteresis    | VBOOT_REFRESH_HYS  |                                                                  | . ( | 0.45 |     | V  |

| General                               |                    |                                                                  |     |      |     |    |

|                                       |                    | VIN=12V, L=120nH<br>EN=3.3V, PWM=800kHz,<br>Duty=15%             | 6   | 5.4  |     | mA |

| VCC Supply                            |                    | VIN=12V, L=120nH<br>EN=3.3V, PWM=500kHz,<br>Duty=15%             |     | 5.4  |     | mA |

| Current Note(1)                       | Ivec               | EN=3.3V, PWM floating<br>BOOT to PHASE=5V, SW short<br>to GND    | 3.2 | 5    | 6.9 | mA |

|                                       |                    | EN=0V, PWM floating<br>BOOT to PHASE=5V, SW short<br>to GND      | 38  | 65   | 92  | μΑ |

|                                       |                    | VIN=12V, L=120nH, EN=3.3V,<br>PWM=800kHz, Duty=15%               |     | 34.7 |     | mA |

|                                       |                    | VIN=12V, L=120nH, EN=3.3V,<br>PWM=500kHz, Duty=15%               |     | 21.7 |     | mA |

| VDRV Supply<br>Current                | Ivdrv              | EN=3.3V, PWM Floating,<br>BOOT short to VDRV, SW<br>short to GND | 180 | 240  | 300 | μA |

|                                       |                    | EN=0V, PWM Floating, BOOT<br>short to VDRV, SW short to<br>GND   | 129 | 184  | 240 | μA |

## **PID3190A**

| LSET Output                        | Vlset             | LSET                                                                    | 1.05 | 1.2 | 1.35 | V  |  |

|------------------------------------|-------------------|-------------------------------------------------------------------------|------|-----|------|----|--|

| LSET                               |                   |                                                                         |      |     |      |    |  |

|                                    |                   | BOOT to PHASE=5V                                                        |      | C   |      |    |  |

| current                            | <b>BOOT2PHASE</b> | V(PWM)=1.65V PHASE=16V,                                                 | 179  | 235 | 291  | μΑ |  |

| BOOT to phase                      |                   | EN=3.3V, VIN=16V,                                                       |      |     |      |    |  |

| SW Pull Down<br>Resistance Note(1) | $R_{SW_{PD}}$     | VCC=VDRV=0V                                                             | 14.7 | 16  | 16.9 | kΩ |  |

| SW Floating<br>Voltage             | Vsw_float         | V(PWM)=1.65V                                                            | 1.2  | 1.4 | 1.7  | V  |  |

|                                    |                   | EN=0V, VIN=15V,<br>V(PWM)=1.65V, BOOT to<br>PHASE=5V, SW short to GND   |      | 34  | 112  | μA |  |

| VIN Bias Current                   | Ivin              | EN=3.3V, VIN=15V,<br>V(PWM)=1.65V, BOOT to<br>PHASE=5V, SW short to GND | 202  | 430 | 659  | μA |  |

Note:

(1) Guaranteed by design or bench characterization data, not tested in mass production.

Potens semiconductor corp.

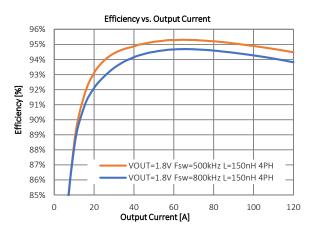

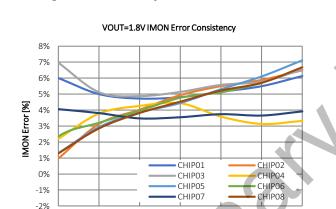

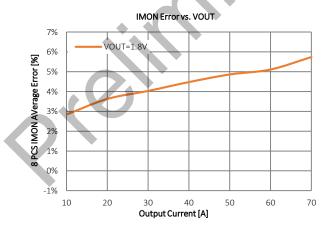

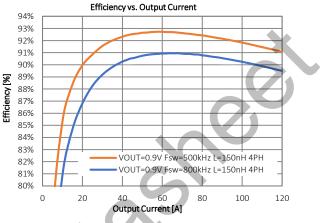

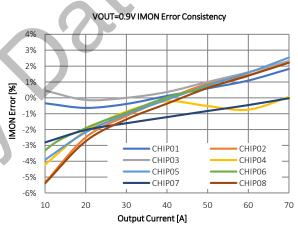

## 9. Typical Performance Characteristics

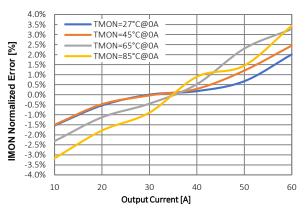

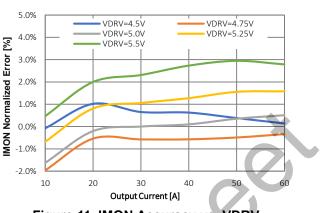

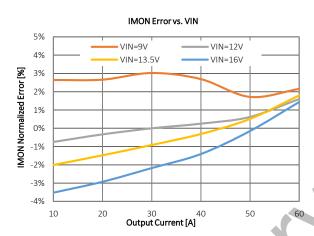

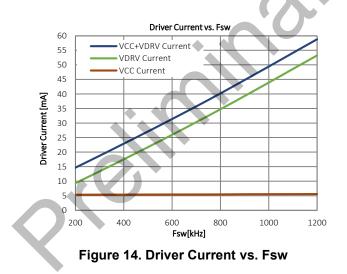

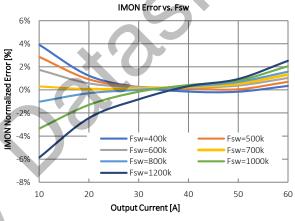

Test conditions: VIN=12V, VCC=VDRV=5V, VOUT=1.8V, LOUT=120nH, Fsw=800kHz, TA=25°C and natural convection cooling unless otherwise specified.

Figure 4. Efficiency Curve for 1.8V VOUT

Output Current [A]

40

50

60

70

Figure 8. IMON Average Accuracy VOUT=1.8V

Figure 5. Efficiency Curve for 0.9V VOUT

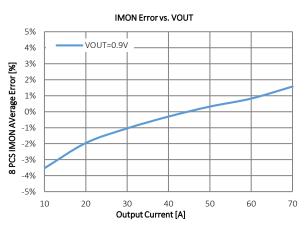

Figure 7. IMON Error Consistency VOUT=0.9V

Figure 9. IMON Average Accuracy VOUT=0.9V

Potens semiconductor corp.

10

20

30

IMON Error vs. VDRV (VCC=VDRV)

Figure 11. IMON Accuracy vs. VDRV

Figure 12. IMON Accuracy vs. VIN

Figure 13. IMON Accuracy vs. Fsw

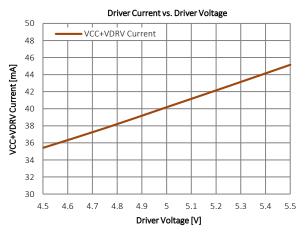

Figure 15. Driver Current vs. Driver Voltage

Potens semiconductor corp.

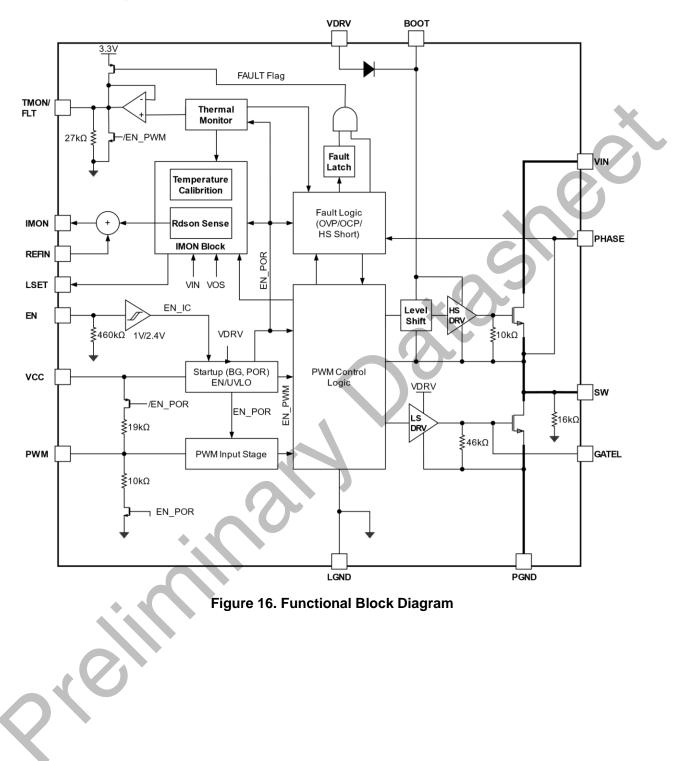

## 10. Block Diagram

## 11. Operation

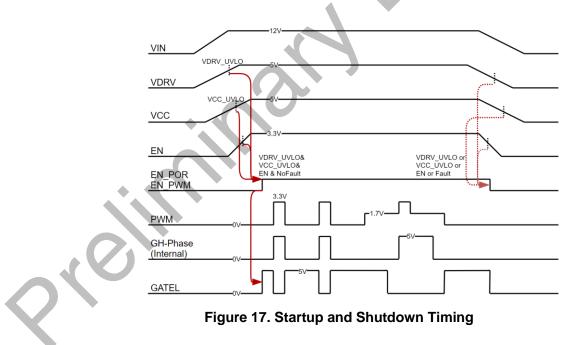

### 11.1 Startup & Shutdown

The PID3190A is enabled by both EN pin input signal and VCC/ VDRV/ BOOT-PHASE UVLO. During VCC UVLO, the driver is fully shutdown (GH, GL=0) and requires 50µs to startup. If VCC is ready and EN is low, the driver is partially shutdown (GH, GL=0) and requires 10µs to startup. If both VCC and EN are ready but VDRV and BOOT-PHASE UVLO, the driver analog circuitry being alive but outputs forced into Tri-state (GH, GL=0). When EN pin is open or pulled down by a PWM controller or an ASIC, the driver goes to sleep mode with very low quiescent current.

| VCC> | VDRV> | BOOT-PHASE> | EN     | Driver State                                 |  |  |  |  |  |

|------|-------|-------------|--------|----------------------------------------------|--|--|--|--|--|

| UVLO | UVLO  | UVLO        |        |                                              |  |  |  |  |  |

| 0    | x     | x           | ~      | Full driver shutdown (GH, GL=0), requires    |  |  |  |  |  |

|      | X     |             | Х      | 50µs for startup;                            |  |  |  |  |  |

| 1    | x     | x           | 0      | Partial driver shutdown (GH, GL=0), requires |  |  |  |  |  |

|      |       |             |        | 10µs for startup                             |  |  |  |  |  |

| 4    | 0     | 0           | 1      | Driver analog circuitry alive but outputs    |  |  |  |  |  |

| 1    | 0     | 0           |        | forced into Tri-state (GH, GL=0)             |  |  |  |  |  |

| 1    | 1     | 1           | 1      | Enabled (GH/GL follows PWM)                  |  |  |  |  |  |

| Х    | Х     | Х           | Open/0 | Disabled (GH, GL=0)                          |  |  |  |  |  |

| Table 1. | UVLO   | and Driver | Truth Table |  |

|----------|--------|------------|-------------|--|

|          | OTEO . |            | math fubic  |  |

Potens semiconductor corp.

#### 11.2 Tri-state PWM Input

The PID3190A features a Tri-state 3.3V/5V PWM input gate drive design. The Tri-state gate drive has logic HIGH, logic LOW and a Tri-state shutdown window. When PWM input signal enters and keeps Tri-state for the defined hold-off time, both GH and GL are pulled low, so that both HSFET and LSFET are turned off, which helps to reduce output overshoot during load release or enter diode emulation mode to increase light-load efficiency. When load releases, multi-phase controller could discharge inductor current with a deeper slope (VOUT + Vdiode)/L, instead of VOUT/L, by sending Low - Tri-state PWM pulse. This reduces overshoot during large load release transient.

| I | EN | PWM       | GH | GL |

|---|----|-----------|----|----|

| ( | 0  | Х         | 0  | 0  |

|   | 1  | Tri-state | 0  | 0  |

|   | 1  | 0         | 0  | 1  |

|   | 1  | 1         | 1  | 0  |

#### Table 2. Tri-state PWM Input Truth Table

#### 11.3 LSET Pin Function

Inductor value setting pin. After VCC is above UVLO, a 1.2V internal voltage source is applied to this pin, the output current is monitored to set inductor starting point for IMON reconstruction algorithm. The inductor value is set by  $1k\Omega/nH$  ratio. If the resistance is less than  $10k\Omega$  or short to GND, L=120nH (default) is set, if this pin is floating, L=210nH is set. The highest inductor value is 1.2uH. To get better IMON performance at startup point, it is recommended to use inductor value matching this calculation result. If not used, left this pin floating or short to GND,

#### 11.4 Current Sensing and Reporting

The PID3190A integrates high accuracy current sense feature, which is based on low-side MOSFET drain source voltage (VDS) when it is on, and a synthesized current when high-side MOSFET is on. The driver incorporates build-in temperature compensation and inductance calibration for current sense to achieve high current sense accuracy and lower propagation delay. The reported current is in the form of current output and the gain is 5 $\mu$ A/A from the IMON pin. In order to convert this current into voltage, a 1 $k\Omega$ , 0.1% resistor is recommended between PWM controller's ISEN and ISENREF pins and this resistor should be placed close to the PWM controller. In order to get a negative current reporting, it is not recommended to set ISENFEF to GND, but to a voltage between 1.1V and 1.9V. If the PWM controller ISEN sampling can accept a current signal, an external 1 $k\Omega$ , 0.1% resistor is not required, and PID3190A IMON pin can be directly connected to the controller's corresponding ISEN pin. PID3190A REFIN pin can be left floating or can be connected to a voltage source between 1.1V and 1.9V.

Potens semiconductor corp.

#### **11.5** Temperature Reporting and Over-Temperature Protection

PID3190A integrates an internal temperature detection circuitry. The sensed temperature is reported at the TMON/FLT pin with a linear voltage slope of 8mV/°C and a 0.6V offset at 0°C. TMON/FLT pin is also used as Faults indication pin, when positive over current protection (POCP), over-temperature protection (OTP), BOOT-PHASE UVLO, LSFET\_SHORT or HSFET\_SHORT occur, by pulling this pin up to 3.3V. When VDRV\_UVLO occurs under power up or normal operation conditions, the TMON/FLT pin is weak pulled down to 0V (or VTMON from other Power Stages in same loop).

When the driver temperature rises higher than 140°C, the TMON/FLT pin will be pulled up to 3.3V and the driver will stop to respond to the controller's PWM. In this way, even if the controller doesn't latch-up and continues to send PWM, the MOSFETs will not switch to prevent the power stage from overheat and affecting long-term reliability. When the driver temperature drops below 120°C, TMON/FLT returns to the voltage value corresponding to driver detected temperature, and the driver starts responding to PWM again.

### 11.6 Positive Over Current Protection

PID3190A features Positive Over Current Protection (POCP) architecture by real-time sensing high-side MOSFET drain source voltage (VDS) when it is on. Once high-side MOSFET real-time sensing current exceeds the POCP threshold, a POCP event is asserted, and the PWM high pulse will be truncated after a short delay so that the high-side MOSFET peak current is almost equal to POCP threshold. If POCP is triggered for 22 consecutive SW cycles, the TMON/FLT pin is pulled up to 3.3V with the driver continuing to respond to PWM. When POCP is not triggered for 3 consecutive SW cycles, POCP event is de-asserted, and TMON/FLT returns to the voltage value corresponding to driver detected temperature.

PID3190A also features a POCP hysteresis circuitry and the typical threshold ( $I_{OC_HYS}$ ) is 10A. In a PWM cycle, PWM is high and POCP is triggered, but when the PWM is low, the valley current value is greater than POCP-  $I_{OC_HYS}$ , then the next PWM high pulse from controller will be ignored and this kind of ignored PWM pulses will not be counted as POCP events. In other words, POCP assertion and de-assertion only counts the number of SW pulses.

#### 11.7 Negative Over Current Protection

In some application scenarios such as DVID (Dynamic Voltage Identification) and OVP (Over Voltage Protection), the low-side MOSFET will be on for a long time to discharge the output energy. If the low-side MOSFET is left on for too long due to incorrectly optimized control loops, the power stage may be damaged because of inductor reverse saturation. Even if the inductor is not reverse saturated, when the low-side is off, this large negative current will pass through the body diode of the high-side MOSFET and may damage the body diode of the high-side MOSFET. In summary, NOCP is necessary.

PID3190A features a Negative Over Current Protection (NOCP) circuitry by real-time sensing low-side MOSFET drain source voltage (VDS) when it is on. Typical threshold is -50A. When the low-side MOSFET real-time sensing current reaches to -50A, the driver will force the low-side MOSFET to be off and high-side MOSFET to be on. But the driver will continue to respond to PWM and report current. There is also a NOCP hysteresis with a typical value of 20A. That is to say when negative current rises to -30A from - 50A, low-side MOSFET will follow PWM levels. Note that NOCP event will not pull high or pull low TMON/FLT pin.

## 11.8 VDRV Undervoltage Lock-out (UVLO)

PID3190A integrates an VDRV UVLO circuitry to actively detect the voltage of the VDRV before power-on and during operation.

Before powering up, if VDRV voltage is below the UVLO threshold (Typical 4.2V), the PWM will be weakly pulled down to GND. This can be used as an indicator signal to tell the PWM controller that the PID3190A is still in VDRV UVLO status. As soon as VDRV voltage exceeds the UVLO threshold, the PWM voltage will change to Tri-state (typical 1.7V) from 0V, indicating that the PID3190A is ready for operation. At the same time, PID3190A will short IMON and REFIN to indicate that it is in UVLO condition.

In normal operation condition, if VDRV UVLO occurs, the device will stop switching. IMON pin, PWM pin and TMON/FLT pin will be pulled down to 0V. PWM pin and TMON/FLT pin are weekly pulled down to GND, so PWM pin voltage can be driven by controller but no switching on Power Stage, and If there are multiple phases connected in the same control loop TMON/FLT pin will continue reporting the highest device temperature.

### 11.9 Bootstrap Capacitor Under-Voltage Protection

PID3190A keeps monitoring the BOOT-PHASE voltage. If EN, VCC and VDRV are ready, but the voltage across the bootstrap capacitor voltage is lower than  $V_{BOOT\_REFRESH\_ON}$  (Typical 3.25V), PID3190A ignores the PWM input signal and starts the boot refresh circuitry. The boot refresh circuitry turns on LSFET for 700ns every 8µs until BOOT-PHASE voltage is above  $V_{BOOT\_REFRESH\_OFF}$  (Typical 3.7V). If the BOOT-PHASE voltage is lower than 3V, then TMON/FLT will be pulled up to 3.3V, IMON/FLT pin is pulled to GND and PID3190A latched up.

Potens semiconductor corp.

#### 11.10 High-side MOSFET and low-side MOSFET Short Protection

This feature reports the damage of high-side MOSFET and low-side MOSFET through TMON/FLT pin. In high output current scenario due to poor output inductor selection or incorrectly optimized control loop, the inductor can be saturated in either the positive or negative direction, which can damage high-side MOSFET or low-side MOSFET.

This function is enabled after the VIN rises above 4V and disabled when VIN falls below 3.65V. When lowside MOSFET is on, the driver continuously monitors the VDS voltage of the low-side MOSFET, so that once this voltage is higher than  $V_{HS_FET_FLT_TH}$  (Typical 0.85V), the high-side MOSFET short event is asserted. When high-side MOSFET is on, the driver continuously monitors the VDS voltage of the highside MOSFET, and once this voltage is higher than  $V_{LS_FET_FLT_TH}$  (Typical 1.75V), the low-side MOSFET short event is asserted. For both high-side MOSFET short and low-side MOSFET short events, TMON/FLT is pulled up to 3.3V in 1 PWM cycle, the driver continuous to respond to PWM commands with IMON pulled up to 3.3V.

#### 11.11 Fault Reporting and Identification

PID3190A features rich protection functions and fault reporting by identification of combinations of PWM, IMON, TMON/FLT status, including:

- VCC\_UVLO and disabled by EN

- VDRV\_UVLO (Before power up and normal operation)

- Positive OCP (POCP, Peak and Valley)

- Negative OCP (NOCP, Peak and Valley)

- BOOT-PHASE UVLO & Refresh

- LSFET Short: HS on (Internal GATEH-PHASE>1V) and VIN-PHASE >1.5V

- HSFET Short: LS on (GATEL>1V) and PHASE-PGND>0.85V

- OTP

**A** .

| Fault Name                           | Fault Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Fault Response                                   | PWM                                                                      | IMON                              | TMON/FLT                                                          |  |

|--------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|--------------------------------------------------------------------------|-----------------------------------|-------------------------------------------------------------------|--|

| VCC_UVLO or disabled by EN           | VCC Undervoltage Lockout<br>or disabled by EN pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                  | High-Z                                                                   | =REFIN<br>By external<br>circuits | High-Z                                                            |  |

| VDRV_UVLO<br>(Power up)              | Driver Undervoltage<br>Lockout                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | latching (PWN                                    | Weak pull down to 0V<br>(PWM pin voltage can<br>be driven by controller, | =REFIN                            | Weak pull down to<br>0V (or VTMON from                            |  |

| VDRV_UVLO<br>(Normal operation)      | Driver Undervoltage<br>Lockout                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                  | no switching on Power<br>Stage)                                          | 0)/                               | other Power Stages<br>in same loop)                               |  |

| POCP (Sourcing)<br>(Peak and Valley) | Peak positive SW current<br>limit; HS FET not turn on if<br>IL> I <sub>OC</sub> - I <sub>OC_HYS</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Cycle-by-Cycle<br>Clamp inductor<br>peak current | Response to PWM                                                          | Continues                         | Assert: 22 cycles to<br>asserted. De-assert:<br>3 OCP-free cycles |  |

| NOCP (Sinking)<br>(Peak and Valley)  | Negative overcurrent: peak<br>negative current threshold<br>that turn off the LSFET                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                  |                                                                          | current                           | Not asserted                                                      |  |

| BOOT_UVLO                            | OT_UVLO<br>Source of the second seco |                                                  | Ignore PWM till<br>BOOT_UVLO clear                                       | 0V when<br>TMON<br>asserted       | Asserted and latch<br>up if lower than 3V                         |  |

| LSFET_SHORT                          | HS on (GATEH-<br>VPHASE>1V) and VIN-<br>VPHASE > 1.75V<br>LS on (GATEL>1V) and<br>VPHASE-VPGND > 0.85V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Continue to<br>respond to PWM<br>commands        | Response to PWM                                                          | =3.3V<br>High Priority            | Asserted and latch<br>up                                          |  |

| OTP                                  | Over Temperature<br>Protection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Shutdown, non-<br>latching                       | Power Stage stops                                                        | REFIN                             | Asserted<br>=3.3V                                                 |  |

## **12. Application**

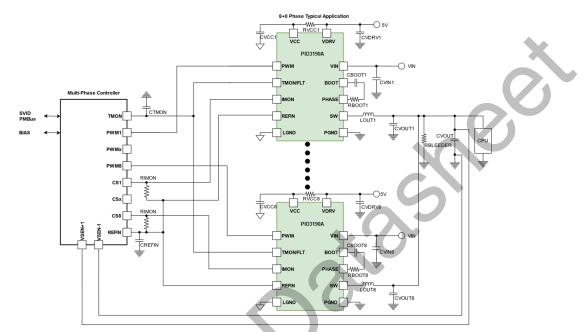

## 12.1 Typical Application

#### Figure 19. Simplified 8 Phase Schematic

#### 12.2 Reference Schematic

Figure 20. Reference Schematic with Notes

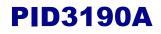

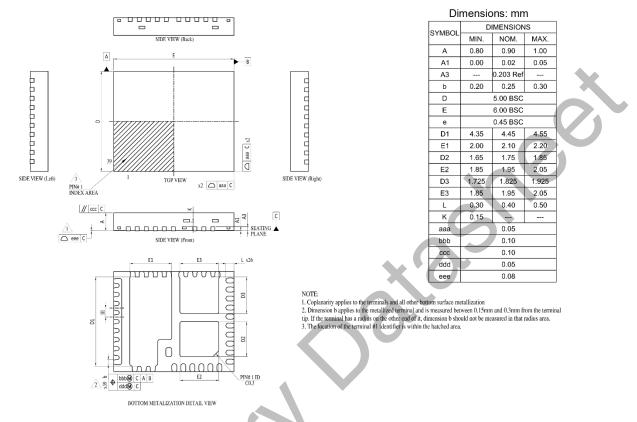

## 13. Mechanical, Packaging

#### 13.1 Package Size

#### Figure 21. Package Size Information

#### 13.2 Solder Resist

Figure 22. Recommended Solder Resist

Potens semiconductor corp.

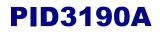

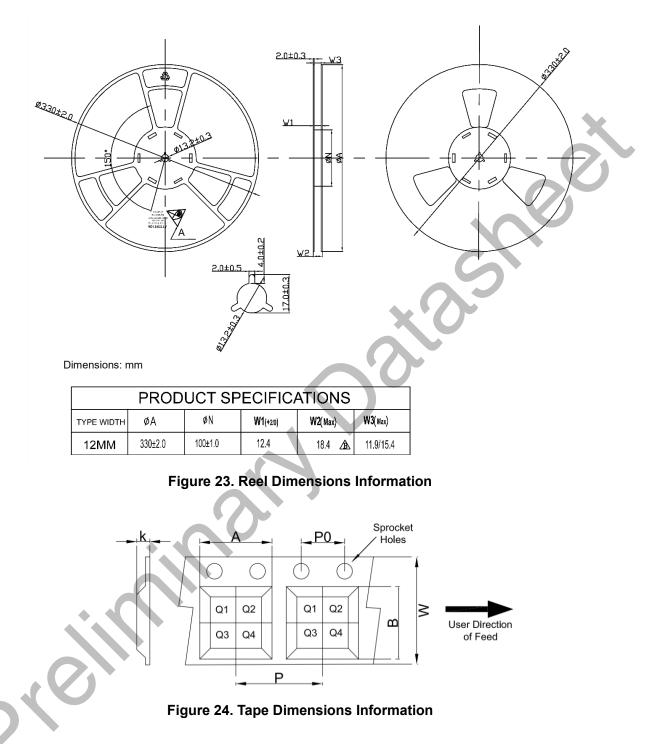

#### 13.3 Reel and Tape Information

#### **Table 4. Tape Dimensions Information**

|  | Device   | Package    | Pins | SPQ   | А       | В       | К       | Р     | P0    | W      | Pin1     |

|--|----------|------------|------|-------|---------|---------|---------|-------|-------|--------|----------|

|  |          | Туре       | PINS | (pcs) | (mm)    | (mm)    | (mm)    | (mm)  | (mm)  | (mm)   | Quadrant |

|  | PID3190A | DFN5X6-39L | 39   | 5000  | 6.3±0.1 | 5.3±0.1 | 1.2±0.1 | 8±0.1 | 8±0.1 | 12±0.3 | Q2       |

**PID3190A**

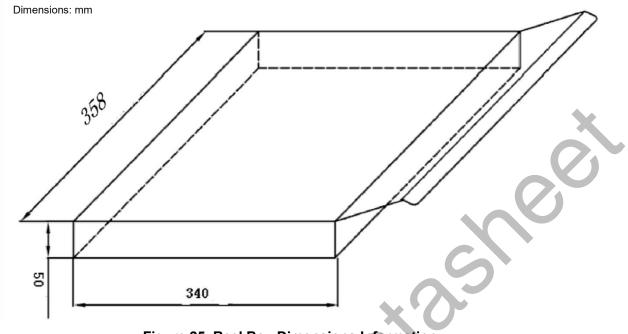

#### 13.4 Reel Box Dimensions

#### Figure 25. Reel Box Dimensions Information

Potens semiconductor corp.