### 第 44 屆中華民國電力工程研討會暨第 20 屆台灣電力電子研討會 運用新特屬應用強化模式模組之金氧半導體場效電晶體 的實現概念於應用效應評估

# A New ASEMM MOSFET Conceptual Realization for Evaluation on Application Effects

游智名 <sup>1</sup> 黄文楠 <sup>1</sup> 陳慶國 <sup>1,\*</sup> 蔡耀文 <sup>1</sup> 李淑惠 <sup>1</sup> Chih-Ming Yu Wen-Nan Huang Ching-Guo Chen Yao-Wen Tsai Shiu-Hui Lee

孟祥集 <sup>1</sup> 羅益民 <sup>1</sup> 張家萱 <sup>1</sup> 張孝惠 <sup>2</sup> 林明贊 <sup>3</sup> Hsiang-Chi Meng I-Ming Lo Chia-Hsuan Chang Sally Chang Ming-Tsan Lin

<sup>1</sup>博盛半導體股份有限公司 Potens Semiconductor Corp. \*Tim@potens-semi.com

<sup>2</sup>源效科技股份有限公司 Powtron Technologies Corp. <sup>3</sup>雅特力科技股份有限公司 Artery Technology Corp.

#### 摘要

為了符合與提供對應電動車、工業自動化、人工智能之伺服器(資料中心)等新應用的需求,本論文提出基於新產品概念稱為 ASEMM 即 Application-Specific Enhanced Mode Module 特屬應用強化模式模組的四個實現案例,來提升金氧半導體場效電晶體 MOSFET 的新競爭力。

分析內容含有 ASEMM 之應用效應:負電壓的效應、效率於全負載域中的平準提升做法、電容運作效果、和 6 合 1(6 in 1)縮減原使用面積達 40%以上的導入設計案等;並整理相關 ASEMM 架構和參數相關理論推導,供研究人員參考與投入這新一代產品概念的實現。

關鍵詞:金氧半導體場效電晶體,特屬應用強化模式 模組

#### **Abstract**

To enrich and meet the further requirement of MOSFET features under recent market new demanding, such as EV implementation, Industrial automation, AI servers/data centers, in this paper, a product strategy differentiating among various MOSFETs through the new conceptual realization by Application-Specific Enhanced (ASEMM) Module to expand competitiveness. Four main concepts are introduced respectively: negative voltage effect, efficiencies leveraging under whole loading condition, capacitor effect, and integration for 6 in 1 MOSFET which is reduced more than 40% area in layout to imply ASEMM's application scenarios for upcoming market trend. Important derivations and the illustration on schemes are also provided for further studying to realize the new generation MOSFET.

Keywords: MOSFET, ASEMM

#### I. 簡介

諸多工業與日常生活應用中,金氧半導體場效電晶 體 (Metal Oxide Semiconductor Field Effect Transistor, MOSFET)在能量或訊號轉換和傳遞上,一直扮演著重 要的關鍵功能;而由該產品應用的類別來區分,除了有 耐高電壓具高效率的 Super Junction MOSFET、高電壓 應用的平面(Planar) MOSFET、低電壓到中電壓的高阻 效(Rsp)溝槽式(Trench)、屏蔽型閘級(Shielded Gate)或分 離型閘級(Split Gate)金氧半導體場效電晶體(SGT MOSFET)等,並有以 MOSFET 應用功能概念為主而導 入的第三代半導體(The 3rd Generation Semiconductors), 如適合於高頻率應用之氮化鎵(Gallium Nitride, GaN)高 電子移動電晶體(High Electron Mobility Transistor, HEMT)及碳化矽 (Silicon Carbide, SiC) MOSFET, 皆再 強化於更嚴苛的高溫高電壓/高電流超高頻率小型化應 用可行性,例如在電動車(Electrical Vehicle, EV)、電動 車充電樁(EV Charger)、人造衛星(Low-Orbit Satellite)、 5G 電信基地台、工業級 PC(Industrial PC, IPC)及伺服器 (Server) 等[1]-[4]。

然為符合衍生的應用要求,進行個別優化的彈性, 博盛半導體股份有限公司和業界相關合作公司已於 2021 年在台灣創新技術博覽會(Taiwan Innovation Exhibition, TIE)提出 ASEMM[5][6],即 Application-Specific Enhanced Mode Module 來作為對應的有效方案, 特屬應用強化模式模組是希望提出一個綜效性的概念, 能夠讓 MOSFET 產生更高的效能,更少的損失,能用 更集約化的設計來減少體積,用更少的元件,產生更多 的智慧化的功能,並用少一些離散設計,多一點的整合, 讓這整個模組發揮最大的效用及在應用上面發揮最大 的功能。總的來說,ASEMM 擁有三項採用的優勢:

一、參數為特用且能有調整的彈性,但是非模組應用 特用化,即模組可在硬體上的元件尺寸(Part Outline Dimension, POD)或封裝(Package)是業界 標準品一致,但特別調整參數後,可以讓同樣的 硬體模組適用於各種不同的應用場合,然其效能 會較原來應用的產品更優化。

- 二、未來能將數位內涵導入到原來的產品設計裡面, 並將參數設定以一定的模型化來運作,可做為調整參數之依據;此亦為運用台灣產品開發技術之 優勢,再植入輕度的軟韌體效能,建立技術門檻, 幫助台灣 MOSFET 產品之加值。

- 三、將以所謂的三高性能(高集成化、高頻化、高效率化)來進行設計規劃,目標在電動車相關應用和人工智慧(Artificial Intelligence, AI)等動能量驅動實踐應用上面,逐步導入第三代半導體扮演應用的材料主軸。

然在許多的 MOSFET 應用之中,電壓的效應與影響的評估,是其中重要的評估項目之一,如應用電壓的額定邊限(Derating)甚或干擾的抗止能力等,都是許多應用上需要的思考和確認來完成評估的工作,本論文將整理基於 ASEMM 的產品概念下,所進行的相關研究觀念推導和案例,供相關研究者參考並期待能加大產、官、學、研界等共同的持續投入。

## II. ASEMM 評估概念一: 驅動整合晶片對 MOSFET 關止負電壓評估[7][8]

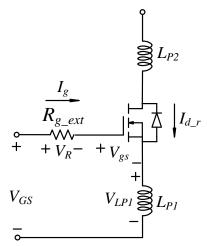

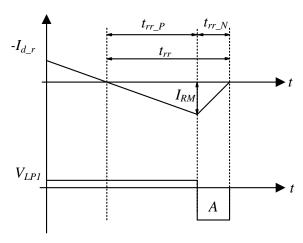

負電壓分析模型如,圖 1 為考慮寄生電感 $L_{P1}$ 效應的 MOSFET 閘極驅動電路與路模型,其中 $V_{GS}$ 為閘極驅動電阻、 $V_R$ 為閘極驅動電阻、 $V_R$ 為閘極驅動電阻電壓、 $I_g$ 為閘極驅動電流和 $V_{gS}$ 為閘源電壓。圖 2 是當 MOSFET 操作在反向恢復期間時,MOSFET 之寄生二極體的反向電流與寄生電感電壓的關係,其中 $I_{d,r}$ 被定義為二極體的電流。 $I_{RM}$ 是二極體的最大反向電流, $t_{rr,P}$ 是感應負電壓的周期。因此,寄生電感的感應負電壓的大小可以推導出如下式:

$$V_{LP1} = L_{P1} \times \frac{dI_{d_{.}r}}{dt} = L_{P1} \times \frac{0 - I_{RM}}{t_{rr_{.}N}} = -L_{P1} \times \frac{I_{RM}}{t_{rr_{N}}}$$

(1)

其中反向恢復電荷 $Q_{rr}$ 、反向恢復時間 $t_{rr}$ 和最大反向電流的關係如下:

$$Q_{rr} = \frac{1}{2} I_{RM} \times t_{rr} \tag{2}$$

而感應負電壓的持續時間影響控制 IC 閘極驅動引腳上的能量應力。感應負電壓持續的時間越長,則控制 IC 就越有可能會被損壞。因此,可以將感應負電壓驅動能量的面積表示為:

$$A = |V_{LP1}| \times t_{rr\ N} \tag{3}$$

將式(1)、式(2)代入式(3),可得到感應負電壓驅動能量的面積如下式:

$$A = 2 \times L_{P1} \times \frac{Q_{rr}}{t_{rr}} \tag{4}$$

上式代表損壞 IC 的能量與反向恢復電荷和反向恢復時間的比率有關。根據上述的關係,可以建立對閘極驅動電路和 MOSFET 等效電路影響的感應負電壓分析

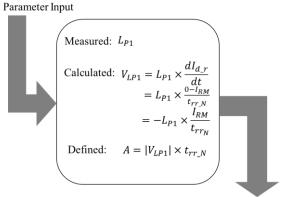

模型,如圖 3 為負電壓分析模型,其中模型的輸入為 MOSFET 參數及根據電路迴路電感測量的寄生參數。 透過這個分析模型,我們可以得到感應負電壓,並根據 這個模型估計感應負電壓對控制 IC 閘極驅動引腳的影響。從圖 1 的閘極驅動電路中,其閘極驅動電壓可重新推導整理如下:

$$V_{GS} = V_{L_{P1}} + V_{R} + V_{gs} = L_{P1} \times \frac{dI_{d.r}}{dt} + V_{gs} + I_{g} \times R_{g} \quad (5)$$

所以上式的閘極驅動電阻增大時,感應負電壓的大小將 減小,如下關係所示:

$$R_a \uparrow \Rightarrow |V_{GS}| \downarrow$$

(6)

由上式可知,感應負電壓越小,閘極驅動感應電壓能量越小。因此,可以透過增加閘極驅動電阻大幅降低 IC 閘極驅動引腳的損壞可能性。

圖 1 带寄生電感的閘極驅動電路

圖 2 汲級電流與感應負電壓之間的關係

Calculated Negative Voltage and Defined Negative Voltage Area w.r.t. time

#### 圖 3 負電壓分析模型

### III. ASEMM 評估概念二:MOSFET 於電磁波干擾降低 的切換電壓波形調整的對應方案[9]

電子電路通常在操作時容易受到電磁干擾(Electro Magnetic Interference, EMI)雜訊的影響而降低工作性能的表現,特別是當電子電路處於倍頻或高頻狀態時,電晶體開關的振鈴也隨之上升,進而產生嚴重的電磁干擾。一般而言,降低電磁干擾的方式有很多種,例如:專利第CN108377095A號「振鈴振幅測量及減輕」,利用峰值檢測器來測量振鈴電壓的振幅,並透過開關驅點器,進一步調整振鈴電壓的振幅,並透過開關驅點器,進而降低電磁干擾,此外,另有其他先前技術可供參考如下:專利第TWI443957B號「高效率電源轉換器系統」、專利第US10498212B2號「Gate driver」等。據此,如何改善電子電路處於倍頻或高頻狀態時,所產生的電磁干擾,進而協助應用電晶體開關的產品在各種負載下,保持優異的電磁干擾調節能力,此乃待須解決之問題。

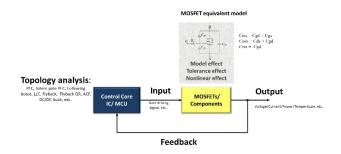

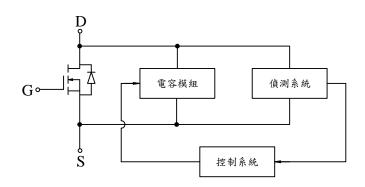

基於 ASEMM 概念下提出一種利用 MOSFET 電容參數的電磁干擾調整器[10],將 MOSFET 當成一般控制系統中的控制對象,如圖 4 所示,透過偵測 MOSFET 的感應電壓和感應電流,依此來推斷 MOSFET 的工作頻率是否處於預設的電磁干擾特別管理頻率內,而當基頻與倍頻關係超過限制時,可以調節外接電容組的內容,以協助應用 MOSFET 的產品在各種負載下,保持優異的電磁干擾調節能力,進而優化電磁干擾的特性。

圖 5 為本文的利用 MOSFET 電容參數的電磁干擾 調整器及方法架構圖,其中電磁干擾調整器的電容模組、 偵測系統及控制系統連接到 MOSFET,而偵測系統可 以偵測 MOSFET 的電壓和電流,控制系統可用微控制 器(Micro Control Unit, MCU)或控制 IC 等同功能之元件 達成。當 MOSFET 運作於電路系統時,透過偵測系統 偵測電流/電壓並反饋至控制系統,若控制系統判斷工 作頻率為非預設狀態,會藉由調控電容模組以調適工作 頻率符合原設定規劃。

圖 4 MOSFET 的系統控制概念

圖 5 利用 MOSFET 電容參數的電磁干擾調整器

由上所述可知,主要透過偵測系統擷取 MOSFET 的電壓及電流,或電容模組的感應電壓和感應電流,依此來推斷 MOSFET 的工作頻率是否處於預設的電磁干擾特別管理頻率內,而當基頻與倍頻的關係超過限制時,可以調節電容模組內多個電容和多個切換開關,透過各個電容的電容參數調整阻抗,進而改變 MOSFET 的電壓上升及下降速度,產生不同的 EMI 量測結果;如此方式據以實施後,確實可達到提供一種協助應用MOSFET 的產品,在各種負載下保持優異的電磁干擾調節能力,進而優化電磁干擾特性,達到電磁干擾調整器的目的。

舉例說明:依據開發經驗 $C_{iss}$ 及 $C_{rss}$ 參數為評估敏感值,並以理論運作阻抗來判斷與推導如下式所示:

$$V_{Noise} \downarrow = \frac{c_{dg} \downarrow}{c_{iss} \uparrow} \tag{7}$$

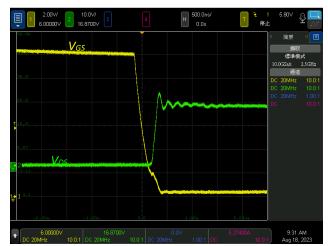

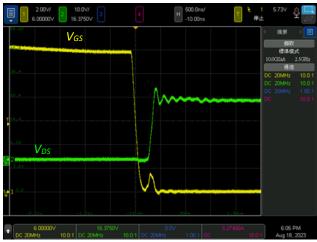

上式是以 $C_{iss}$ 為主連結參數, $C_{iss}$ 會影響波形 1 turn OFF 時 $V_{GS}$ 波形(當 $C_{iss}$ 越大, $V_{GS}$  OFF 的波形斜率越緩)及與波形 2 的 $V_{GS}$ 突波的重疊程度關係,如表 1 為 MOSFET  $V_{GS}$ 的波形合成圖。圖 6 為 MOSFET 1 具有較大 $C_{iss}$ 的實測波形,因 $V_{GS}$  OFF 斜率較緩並已含疊入了大波份的 $V_{GS}$ 突波,因此在波形中顯現微小的突波,圖 7 為MOSFET 2 具有較小 $C_{iss}$ 的實測波形, $V_{GS}$ 突波則為明顯的顯現,由兩者的波形比較可以看出 $C_{iss}$ 越大, $V_{GS}$  OFF的波形斜率越緩關係,則其 EMI 測試結果會較好。

表 1 MOSFET 的 V<sub>GS</sub>波形合成圖

| MOSFET | MOSFET 1                                                                           | MOSFET 2                                                              |

|--------|------------------------------------------------------------------------------------|-----------------------------------------------------------------------|

| 說明     | Ciss 較大,會造成 $V_{GS}$ OFF 波形<br>較緩 $\cdot$ OFF 時間較長 $\cdot$ 也易將 $V_{GS}$<br>突波含入並重疊 | Ciss 較小, $V_{GS}$ OFF 波形較陡,<br>OFF 時間較短 $\cdot$ 不易將 $V_{GS}$ 突波<br>含八 |

| 波形     | 渡形1: VGS由ON職OFF波形<br>(科率較緩)<br>液形2 VGS<br>的突波                                      | 波形1: VGS由ON轉OFF波形<br>(斜年取限)<br>X克积2-VGS<br>内突波                        |

圖 6 MOSFET 1 具有較大Ciss的實測波形

圖 7 MOSFET 2 具有較小Ciss的實測波形

## IV. ASEMM 評估概念三: MOSFET 於系統輕重負載效率提升的耐受電壓調整的對應方案[11]

有關如何有效提高輕負載效率並非新的議題,如專利第 CN102904424B 號提出一種具有提高輕負載效率的開關調節器,其包含有控制器、多相降壓轉換器和輔助低功率相。控制器為控制多相降壓轉換器以及輔助相的操作。多相降壓轉換器包括有複數個主相,其被配置為將輸入電壓轉換成較低電壓,以施加到不同負載狀態下的電子設備,以此將小量輸出電流輸送到輕負載狀態

下的電子設備,增加開關調節器在輕負載狀態下效率。雖然與先前無提高輕負載效率開關調節器時,能有效地降低由重載切換至輕載時的能源損耗,但由於此發明需具有複數個主項,如此將會使控制開關具有較大的體積及成本,而會面臨無法達到輕量、簡便、低成本的問題。

為有效提升電晶體在輕載情況下之使用效率,以及降低電晶體體積、成本以及開關耗損,本文使用一種具非對稱並聯裸晶的 MOSFET,藉由其負載電感在變化時產生電壓資訊,再由負載辨識控制單元對開關進行控制,意即可以在不同的負載情況下由不同的裸晶進行控制。本文之電晶體包含有電感、負載辨識控制單元、兩裸晶(第一裸晶及第二裸晶,其中第一裸晶大於第二裸晶)以及閘級信號選擇切換開關。

此方案主要目的在於提供一種具非對稱並聯裸晶 的 MOSFET,其特點為可依據負載大小調整導通的裸 晶使其使用效率最佳化。具非對稱並聯裸晶的 MOSFET 為包含有相互電性連接的 MOSFET(具有第一裸晶、第 二裸晶以及開關)、負載辨識控制單元及電感。根據歐 姆定律,當負載大小不同通過電感的電流亦會隨之改變, 又根據電磁感應定律,電感之電壓訊號會透過電流變化 而感應出,並藉此電壓訊號使負載辨識控制單元來調控 閘級信號開關,使第一裸晶、或第二裸晶導通或斷路, 其中,第一裸晶大於第二裸晶。於重負載時,通過較大 的第一裸晶導通,由於在重負載時,具非對稱並聯裸晶 的 MOSFET 的導通損耗較驅動損耗占比更大,故利用 第一裸晶進行導通相較利用第二裸晶,功率的耗損較低。 於輕載時,通過第二裸晶進行導通,由於第二裸晶為較 小的裸晶,可利用較小的閘極驅動電壓進行驅動,降低 了具非對稱並聯裸晶的 MOSFET 的驅動損耗及整體功 率的損耗。實現方式如上所述,藉此方式能達到兼顧體 積、成本,並使效率最佳化,圖8為非對稱並聯裸晶的 MOSFET .

圖 8 為非對稱並聯裸晶的 MOSFET

### V. ASEMM 評估概念四:MOSFET 於馬達驅動應用中 同電壓要求下的集成對應方案

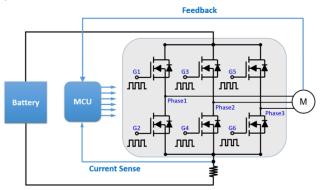

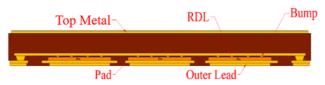

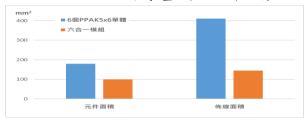

在產品應用的評估上,縮小體積為眾多產品使用者的期待趨勢,而採用了 ASEMM 的實現概念,博盛半導體股份公司在馬達驅動應用上提出六合一(6 in 1)的 MOSFET 模組,如圖 9 所示,將六個 MOSFETs 的驅動元件整合在一個特屬應用強化模式模組,其運用重布層

第四十四屆中華民國電力工程研討會暨 第二十屆台灣電力電子研討會 台灣 臺北市 2023 年 12 月 1-2 日

式(Redistribution Layer, RDL)的封裝方式,如圖 10 所示,在主架構內實現無內打線(Wire Bonding, WB)的設計,並運用銅傳柱(Copper Pillar)的雙面強化導熱路徑,如圖 11,架構基於芯(晶)片與散熱基架(Lead Frame)絕緣的處理後的導熱優勢,且能以極薄 0.6mm 的集成應用實施例於三相式的馬達驅動電路達驅動產品中,而因驅動元件小體積集成的優勢,如圖 12 為 6 個 PPAK5×6 MOSFET 單體面積與六合一 MOSFET 模組面積及整體佈線面積比較圖,可以使其有機會結合在馬達本體上,能將電路板內置在馬達中,為系統產品提供體積及散熱領先優勢。

鑑於近年來消費性電子產品的應用廣泛,加上車用市場將接續消費電子市場需求數量上升,MOSFET之市場愈發蓬勃,因應市場的需求必須不斷進步及改善,例:消費性電子使用之快充,因使用者對充電效率要找提升,故高功率、體積小之 MOSFET 成為快充最佳之材料。因此成本、體積及有效的能源使用更成為市場競爭的主要因素。雖有效提高輕負載效率並非新的議題,但先前的文章並未考慮到體積以及成本的問題,因因此本文一並考慮了體積、成本以及能源的使用效率之問題,本文的方法為利用電感在負載變化時產生電壓資訊,再由負載辨識控制單元對開關進行控制,使其在不同連出數辨識控制單元對開關進行控制,使其在不同通狀況下由不同裸晶進行導通,以達到將使用能源效率最佳化。

圖 9 馬達驅動應用六合一的 MOSFET 模組

圖 10 重布層式的封裝架構

圖 11 雙面強化導熱封裝內部架構及元件背面

圖 12 六合一模組與 6 個 PPAK5X6 單體之元件面積與整體佈線面積比較

#### VI. 結論

ASEMM可以協助將 MOSFET 提升三高化的特色, 高集成化、高頻化、高效率化。而高集成化跟高頻化, 偏屬於同一個趨勢,但是要跟高效率化連結時,會需要 特別材料的優勢,而第三代半導體是未來 ASEMM 的 主要導入材料。

在高集成化的實現,在智慧系統運用上非常具有優勢。高頻化上,可產生適用於實現在高效率電路如Totem pole PFC,在智慧快速充電樁的應用上是一項特色。在高效率化上,導入 TOLL 封裝的 ASEMM 是明確方向,可應用於電動車的次系統,例如智慧電池的管理應用中,這在汲源極間(Drain to Source)的導通阻抗可下降,在智慧電池管理應用上面是一個值得的研究方向。

#### 参考文獻

- [1] H. Fujita, H. Akagi and S. Shinohara, "A 2-MHz, 6-kVA voltage-source inverter using low-profile MOSFET modules for low-temperature plasma generators", PESC 98 Record. 29th Annual IEEE Power Electronics Specialists Conference, Fukuoka, Japan, 22-22 May 1998, pp. 153-158.

- [2] J. G. Bai, G. Q. Lu and X. Liu, "Flip-Chip on Flex Integrated Power Electronics Modules for High-Density Power Integration", IEEE Transactions on Advance Packaging, Vol. 26, No. 1, pp. 54-59, Feb., 2003.

- [3] Y. C. Son, K. Y. Jang and B. S. Suh, "Integrated MOSFET inverter module for low-power drive system", Twentieth Annual IEEE Applied Power Electronics Conference and Exposition, Austin, USA, 6-10 Mar. 2005, pp. 1048-2334.

- [4] H. Li, S. Munk-Nielsen, X. Wang, S. Bęczkowski, X. Wang, S. R. Jones and X. Dai, "Effects of Auxiliary-Source Connections in Multichip Power Module", IEEE Transactions on Power Electronics, Vol. 32, No. 10, pp. 7816-7823, Oct., 2017.

- [5] https://www.digitimes.com/news/a20211011VL201.html

- [6] https://tie.twtm.com.tw/zh-tw

- [7] C. G. Chen, S. H. Lee, C. M. Yu, W. N. Huang, J. S. Lee, H. C. Meng and T. M. Lai, "Negative Voltage Analysis Model for Evaluation on Control IC Driving of MOSFET Application", in 4th International Conference on Microelectronic Devices and Technologies (MicDAT '2022), Corfu, Greece, 21-23 Sep. 2022, pp. 5-8.

- [8] C. G. Chen, S. H. Lee, C. M. Yu, W. N. Huang, J. S. Lee, H. C. Meng, T. M. Lai, "Evaluation on Negative Voltage Analysis Model for Gate Driving of MOSFET Application", Sensors & Transducers, vol. 259, no. 5, pp. 75-81, 2022.

- [9] 專利第TWI790701號"利用場效電晶體電容參數的電磁 干擾調整器及方法"。

- [10] 黃文楠、吳英秦、方志行、陳俊成、鄧清政、陳思翰,"基 於相關係數概念之電性測試規劃探討",2006 中國電工 技術學會電力電子學會第十屆學術年會論文。

- [11] 專利第TWI798777號"具非對稱並聯裸晶的金氧半場效 電晶體及其實施方法"。